半導体設計の未来を拓く図研の提案

株式会社図研は、2025年12月17日(水)から19日(金)にかけて開催される「SEMICON Japan 2025」に出展し、半導体の前工程と後工程を統合する革新的な設計環境を提案します。この取り組みは、テクノロジーパートナーであるSynopsys社との協調ソリューションを強化することで実現され、半導体業界が直面する課題解決に貢献することが期待されています。

半導体業界が直面する課題と新たな潮流

現在、半導体業界は、微細化技術による性能向上に限界を迎えつつあります。この状況を打破するため、チップレットや3DIC(三次元集積回路)といった後工程技術への期待が急速に高まっています。しかし、これらの技術を実用化するには、半導体の前工程と後工程を密接に連携させ、チップ、インターポーザー(中間基板)、パッケージを含むシステム全体を統合的に設計・解析できる環境が不可欠です。

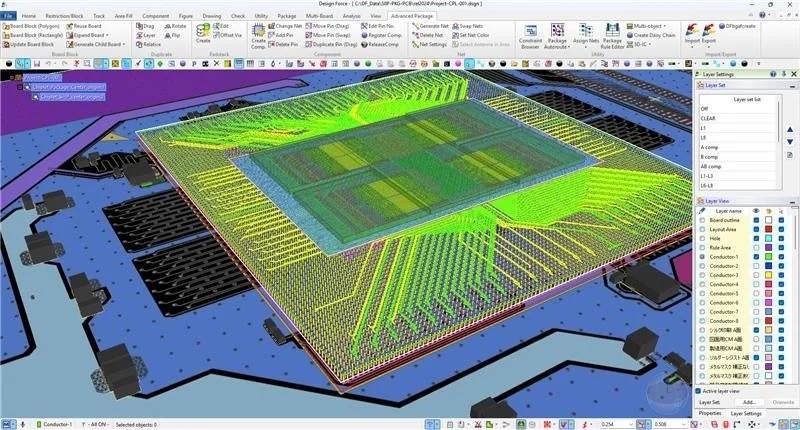

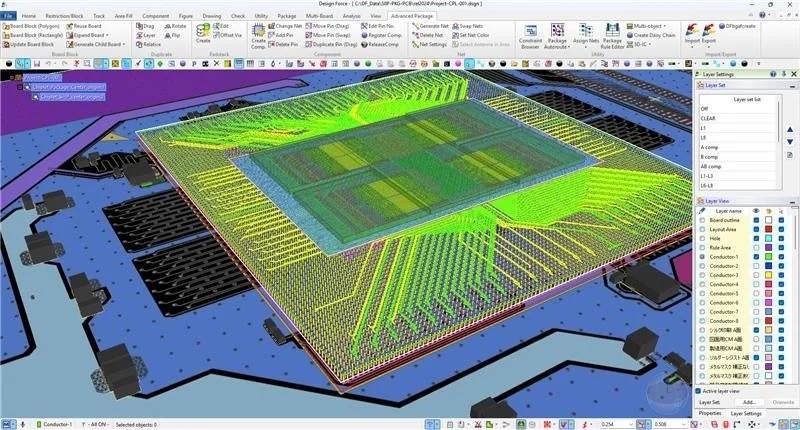

図研の統合設計・解析環境「CR-8000 Design Force」

図研は、システムレベルのマルチボード設計環境「CR-8000 Design Force」において、長年にわたり3次元データベースを採用してきました。これにより、SoC(System on Chip)、パッケージ、PCB(プリント基板)といった異なるテクノロジーを持つ複数のオブジェクトを、一つのシステムとして統合的に設計・検証できる環境を提供しています。この実績を活かし、インターポーザーを含む半導体アドバンスドパッケージの設計環境としてのパフォーマンスをさらに強化しています。

テクノロジーパートナーとの連携

「CR-8000 Design Force」は、テクノロジーパートナーであるSynopsys社の「3DIC Compiler」やAnsys社の解析ソリューションとシームレスに連携します。これにより、従来の分業化による制約や技術的な課題を解消し、半導体の前工程と後工程を統合する設計解析環境の実現を目指しています。

SEMICON Japan 2025での展示内容

図研ブースでは、以下のソリューションが紹介されます。

-

半導体アドバンスドパッケージ設計を含むシステムレベル設計・検証支援: 「CR-8000 Design Force」による最先端の設計フローが展示されます。

-

半導体製造装置開発支援: 図研の電装設計ソリューションが、製造装置開発の効率化にどのように貢献するかを紹介します。

-

パートナー企業によるプレゼンテーション: Synopsys社、Ansys社による最新技術に関するプレゼンテーションも予定されています。

仮屋和浩氏がパネルディスカッションに登壇

図研の専務執行役員 CTO 技術本部長である仮屋和浩氏が、以下のパネルディスカッションに登壇します。最新の業界トレンドや技術について深く掘り下げた議論が展開されるでしょう。

| パネルディスカッション名 | 日時 | 会場 | テーマ |

|---|---|---|---|

| APCS2025 パネルディスカッション | 2025年12月18日(木) 14:30 ~ 16:35 | SuperTHEATER(西4ホール内) | 未来をつなぐチップレット:光・車・AIが描くサステナブル社会 |

| ADIS2025 パネルディスカッション | 2025年12月18日(木) 9:30~11:00 | TechSTAGE SAKURA(会議棟 605-606) | 徹底討論『設計のAI活用』と『デジタルツイン』~EDA・半導体ベンダが語る設計現場の最前線 |

パネルディスカッションの詳細については、以下のリンクから確認できます。

「SEMICON Japan 2025」出展概要

図研の出展に関する詳細は以下の通りです。

| 項目 | 詳細 |

|---|---|

| 展示会名 | SEMICON Japan 2025 |

| 日時 | 2025年12月17日(水)~19日(金) 10:00~17:00 |

| 会場 | 東京ビックサイト 東ホール |

| 展示内容 | ・ Zuken/Synopsys/Ansys テクノロジーアライアンスで実現する半導体アドバンスドパッケージの統合設計・解析環境 |

| 公式サイト | SEMICON Japan 2025 |

図研は、この出展を通じて、半導体設計の新たな可能性を広げ、業界全体の発展に貢献していくことでしょう。詳細情報は図研のウェブサイトでも確認できます。